- Home

- Documentation

- Community

- Projects

- Boards

- Agilex 5 SoC

- Agilex 7 SoC

- Arria 10 SoC

- Nallatech 385A - Arria 10 FPGA Network Accelerator Card

- Nallatech 385A-SoC Accelerator Card with Arria 10 FPGA

- ALARIC Instant DevKit ARRIA 10 SoC FMC IDK by REFLEX CES

- Altera Arria 10 SoC Virtual Platform

- Altera Arria 10 SoC Board

- Nallatech 510T compute acceleration card with Intel Arria 10 FPGA

- REFLEX CES Achilles Arria 10 SoC SOM

- Terasic Arria10 SoC Board : HAN Pilot Platform

- Arria V SoC

- Cyclone V SoC

- Altera Cyclone V SoC Board

- Arrow SoCKit User Manual - July 2017 Edition

- Arrow SoCKit User Manual - November 2019 Edition

- Arrow SoCKit Evaluation Board

- Atlas-SoC Development Platform

- Critical Link MitySOM-5CSx Development Kit

- Cyclone V Ethernet driver problems

- DE10-Nano Development Board

- Terasic DE10-Standard Development Kit

- Devboards DBM-SoC1 module

- Devboards DBM-SoC2 module

- EBV SoCrates Evaluation Board

- Enclustra Mercury SA1 SoC Module

- Enterpoint Drigmorn 5

- Enterpoint Larg 2

- Altera Cyclone V SoC Development Platform

- Mpression Helio SoC Evaluation Kit by Macnica

- Mpression Sodia Evaluation Board by Macnica

- ARIES Embedded - MCV System on Module

- Mpression Borax SOM Module and Development Kit by Macnica

- Enterpoint Mulldonoch 3

- Networked Pro-Audio FPGA SoC Development Kit by Coveloz

- NOVPEK™CVLite

- NOVSOM®CV

- NOVSOM®CVLite

- NovTech IoT Octopus™

- NovTech NetLeap™

- Enterpoint Raggedstone 4

- Solectrix SMARC compliant System-on-Module

- Terasic DE1-SoC Development and Education Board

- Stratix 10 SoC

- Find a Board

- News

Projects

Similar topics

-

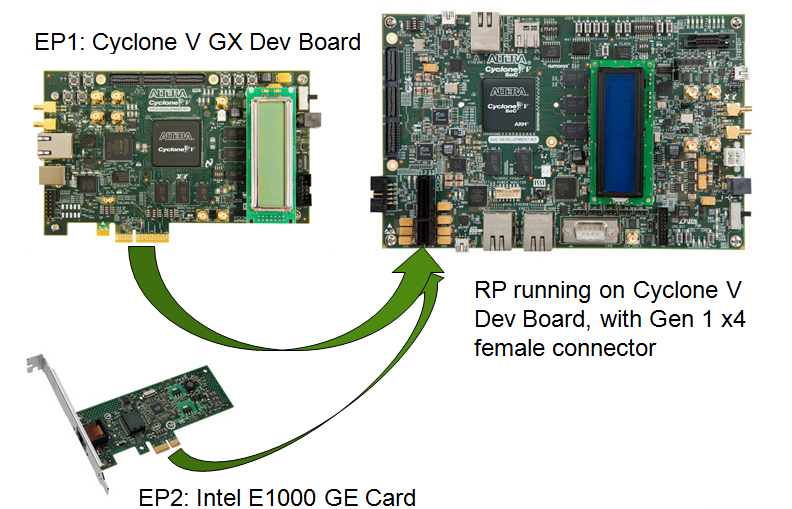

PCIe Root Port with MSI

An example which implements a PCIe root port on an Altera Cyclone V SoC development board and a PCIe end point on a Cyclone V development board

-

Arria V PCIe Root Port with MSI

An example which implements a PCIe root port on an Altera Arria V SoC development board

-

OpenCL Mandelbrot Demo on Sodia

This is a design example using Sodia board by Apollo Giken(Altera DSN partner in Yokohama,Japan).

-

Multi-channel PWM Design using Macnica Helio.

This design demonstrates how to utilize the Macnica Helio SoC board to add multi channel PWM (pluse width modulation) device.

-

Datamover Design Example

Datamover example design sets to demonstrate design practices and software solutions to achieve high performance real time application with HPS ARM processor.

Recent Changes

-

Intel® Agilex® 7 I-Series Transceiver-SoC Development Kit (4x F-Tile) System Example Design With IEEE1588 PTP (25GE/10GE 2-Port)

Intel® Agilex® 7 I-Series Transceiver-SoC Development Kit (4x F-Tile) System Example Design With IEEE1588 PTP (25GE/10GE 2-Port)

-

Multiprocessor Nios V/m system: creating your first GeMRTOS application

Quick Start Guide on how to create a multiprocessor system with Nios V processor and GeMRTOS support

Multiprocessor Nios V/m system: creating your first GeMRTOS application

Quick Start Guide on how to create a multiprocessor system with Nios V processor and GeMRTOS support -

Setting up and Using Bridges on Agilex 7 SoC

Setting up and Using Bridges on Agilex 7 SoC

-

Agilex 7 SoC With eMMC Storage On HPS

Agilex 7 SoC With eMMC Storage On HPS

-

Stratix 10 SoC with eMMC Storage on HPS

Stratix 10 SoC with eMMC Storage on HPS

Table of Contents

An example which implements a non-MSI PCIe root port on an Altera SoC development board

An example which implements a non-MSI PCIe root port on an Altera SoC development board

| Board: | AlteraSoCDevelopmentBoard |

|---|---|

| State: | planned |

| Members: | LFTAN, RocketHwong |

Please refer to this project for updated PCIe example design with MSI support

This example shows functionality of the HIP PCIe root port with HPS (ARM) as the host processor. It shows the entire design flow from Qsys/Quartus-II to device tree handoff to Linux application access.

There are two hardware configurations. The first configuration demonstrates DMA transfer throughput over PCIe Gen1 x4 link from either RP (read/write) or EP (read/write). The second configuration simply enumerates and configures an off-the-shelf PCIe Ethernet card to show general compatibility.

Application Note

This document describes how to use the PCIe Root Port design example on an Altera Cyclone V Development Board. The design example consists of Qsys projects and Linux software, which can be downloaded as described in the following sections.Qsys Projects

Three different root port Qsys designs are included for different size requirements (full, simplified, small).Software

This tar file includes all the source and binaries for Linux RP driver, EP driver, and Linux benchmark app.© 1999-2024 RocketBoards.org by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

This website is using cookies. More info.

That's Fine

RocketBoards

RocketBoards